# RISC (MIPS, RISC-V) and CISC (x86) Instruction Sets

Jaynarayan T Tudu

Lecture 6

IIT Tirupati, India 13<sup>th</sup> Feb, 2020 Computer System Architecture

Jaynarayan T Tudu RISC (MIPS, RISC-V) and CISC (x86) Instruction Sets

- Introduction and recent trends in Computer Architecture

- Fundamentals of Computer System Design

- Measuring Performances: Benchmark and Metric

- Analysis of Instructions

- Addressing modes

Important features of RISC architecture.

- Simple instructions

- Fixed Instruction Encoding

- Simple controller

- Load/Store architecture (is this good or bad?)

- Instruction count increases

- Limited addressing modes

Desktop and Server:

- Digital Alpha

- MIPS, Inc.

- Hewlett-Packard PA-RISC

- IBM and Motorola PowerPC

- Sun Microsystems SPARC

Embedded Computing and Mobile Devices:

- Advanced RISC Machines ARM

- Advanced RISC Machines Thumb

- Hitachi SuperH

- Mitsubishi M32R

- MIPS, Inc. MIPS16

The emphasis of MIPS architecture:

- A simple load-store instruction set

- Designed for pipe-line efficiency

- Fixed instruction encoding

- Efficiency as compiler target

Classification of registers:

- General purpose registers (Integer registers)

- Floating point registers

- Special purpose registers

General purpose registers also known as Integer register: Size 64 bits

| 63  | 0 |

|-----|---|

| R0  |   |

| R1  |   |

|     |   |

| R31 |   |

Classification of registers:

- General purpose registers (Integer registers)

- Floating point registers

- Special purpose registers

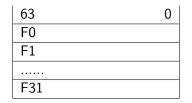

## Floating point register:

Size 64 bits: it support single and double-precision

## Usage of registers

| R0        | Hard-wired to 0                                                  |  |  |

|-----------|------------------------------------------------------------------|--|--|

| R1        | Reserved for pseudo-instructions                                 |  |  |

| R2 - R3   | Return values from functions                                     |  |  |

| R4 - R7   | Arguments to functions - not preserved by subprograms            |  |  |

| R8 - R15  | Temporary data, not preserved by subprograms                     |  |  |

| R16 - R23 | Saved registers, preserved by subprograms                        |  |  |

| R24 - R25 | More temporary registers, not preserved by subprograms           |  |  |

| R26 - R27 | Reserved for kernel. Do not use.                                 |  |  |

| R28       | Global Area Pointer (base of global data segment)                |  |  |

| R29       | Stack Pointer                                                    |  |  |

| R30       |                                                                  |  |  |

|           | Frame Pointer                                                    |  |  |

| R31       | Return Address                                                   |  |  |

| F0 - F3   | Floating point return values                                     |  |  |

| F4 - F10  | Temporary registers, not preserved by subprograms                |  |  |

| F12 - F14 | First two arguments to subprograms, not preserved by subprograms |  |  |

| F16 - F18 | More temporary registers, not preserved by subprograms           |  |  |

| F20 - F31 | Saved registers, preserved by subprograms                        |  |  |

## Integer:

- 8-bit (byte)

- 16-bit (half word)

- 32-bit (word)

- 64-bit (double word)

Floating-point:

- 32 bit single precision

- 64-bit double precision

MIPS64 addressing mode for data transfer:

- It has only three type of addressing modes

- I type: Immediate

- R type: Register-register

- J type: Jump (Offset added to PC, index mode)

However indirectly supports:

- Displacement mode

- Register indirect

- Absolute addressing

## Addressing Modes for MIPS

## Three type of addressing modes with fixed operands:

### I-type instruction 6 5 5 16 Opcode rs rt Immediate

Encodes: Loads and stores of bytes, half words, words, double words. All immediates (rt - rs op immediate)

Conditional branch instructions (rs is register, rd unused) Jump register, jump and link register

(rd=0, rs=destination, immediate=0)

R-type instruction

Register-register ALU operations: rd – rs funct rt Function encodes the data path operation: Add, Sub, . . . Read/write special registers and moves

### J-type instruction

Jump and jump and link Trap and return from exception With respect to Memory:

- Byte addressable

- 64 bit address space

- Mode bit for Big and Little support (this is good)

- All the memory access must be aligned (why?)

## Instruction Format for MIPS

#### I-type instruction

| 6      | 5  | 5  | 16        |

|--------|----|----|-----------|

| Opcode | rs | rt | Immediate |

Encodes: Loads and stores of bytes, half words, words, double words. All immediates (rt - rs op immediate)

Conditional branch instructions (rs is register, rd unused) Jump register, jump and link register

(rd=0, rs=destination, immediate=0)

R-type instruction

| 6      | 5  | 5  | 5  | 5     | 6     |  |

|--------|----|----|----|-------|-------|--|

| Opcode | rs | rt | rd | shamt | funct |  |

Register-register ALU operations: rd – rs funct rt Function encodes the data path operation: Add, Sub, . . . Read/write special registers and moves

#### J-type instruction

Jump and jump and link Trap and return from exception

## Instructions are of 32 bit length.

Jaynarayan T Tudu RISC (MIPS, RISC-V) and CISC (x86) Instruction Sets

Broadly operations are classified in four:

- Load and Store operations

- ALU operations

- Is Branch and Jump operations

- Is Floating point operations

| Load double word   |

|--------------------|

| Load double word   |

| Load word          |

| Load byte          |

| Load byte unsigned |

| Load FP single     |

| Load FP double     |

| Store double word  |

| Store word         |

| Store half         |

| Store byte         |

| Store FP single    |

| Store FP double    |

|                    |

| DADDU R1, R2, R3  | Add unsigned           |

|-------------------|------------------------|

| DADDIU R1, R2, #3 | Add immediate unsigned |

| LUI R1, #42       | Load upper immediate   |

| DSLL R1, R2, #5   | shift left logical     |

| SLT R1, R2, R3    | Set less than          |

- Instruction with Immediate Operands: ADDI, ADDI ADDIU, ANDI, LUI, ORI, SLTI, SLTIU, XORI

- Three operand instructions: ADD, ADDU, AND, NOR, OR, SLT, SLTU, SUB, SUBU, XOR

- ALU Two operand Instruction: CLO, CLZ, NOR, OR, XOR

- Shift instructions: SLL, SLLV, SRA, SRAV, SRL, SRLV

- Mutiply and Divide: DIV, DIVU, MADD, MADDU, MFHI, MFLO, MSUB, MSUBU, MTHI, MTLO, MUL, MULT, MULTU

- J name  $PC_{36,...,63} \leftarrow name$

- JAL name  $Regs[R31] \leftarrow PC + 8; PC_{36...63} \leftarrow name$

- JALR R2 Regs[R31]  $\leftarrow$  PC + 8; PC  $\leftarrow$  Reg[R2]

- JR R3 PC  $\leftarrow$  Reg[R3]

- BEQZ R4, name if R4 == 0 then PC  $\leftarrow$  name

- BNE R3, R4, name if R3 != R4 then PC  $\leftarrow$  name

- MOVZ R1, R2, R3 if R3 == 0 then R1  $\leftarrow$  R2

## The principle:

- Manipulates the floating point registers

- Indicate the operation to be single or double precession

- FP addition: ADD.S and ADD.D

- FP subtraction: SUB.S and SUB.D

- FP multiplication: MUL.S and MUL.D

- FP division: DIV.S and DIV.D

- FP comparison: C.X.S and C.X.D

- FP branch true:BCLT and branch false: BCLF

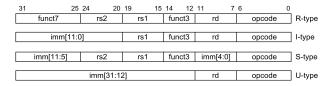

## Instruction set format:

The RISC-V has four different format of fixed length. This is very similar to MIPS where it has three isntruction format. Valid question: Why did RISC-V chose additional instruction format?

## Description of instruction set format:

| Instruction<br>format | Primary use                                | rd                                       | rs1                                             | rs2                                      | Immediate                        |

|-----------------------|--------------------------------------------|------------------------------------------|-------------------------------------------------|------------------------------------------|----------------------------------|

| R-type                | Register-register<br>ALU instructions      | Destination                              | First source                                    | Second source                            |                                  |

| I-type                | ALU immediates<br>Load                     | Destination                              | First source base<br>register                   |                                          | Value<br>displacement            |

| S-type                | Store<br>Compare and<br>branch             |                                          | Base register first source                      | Data source to<br>store second<br>source | Displacement<br>offset           |

| U-type                | Jump and link<br>Jump and link<br>register | Register<br>destination for<br>return PC | Target address for<br>jump and link<br>register |                                          | Target address for jump and link |

The RISC-V has four different format of fixed length. This is very similar to MIPS where it has three isntruction format. Valid question: Why did RISC-V chose additional instruction format?

The riscv classify instructions into four classes:

- Load/store

- Control

- ALU

- Appendix A of text book: Henessy and Patternson, Computer Architecture Quatitative Approach, 5th Edition

- Appendix K of text book: Available online.

- Relevant Papers on MIPS32 and MIPS64

thank you